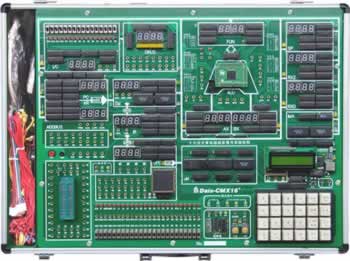

现代计算机组成原理与系统实验箱(16位)

- 型号:TRY-CMX16+

- 品牌:上海荣育

- 所在地:上海

- 供货总量:大量供货

- 发货期限:商定

- 价格:询价元

- 电话:021-63811399 / 021-53550259

TRY-CMX16+现代计算机组成原理与系统实验箱(16位)

一、现代计算机原理与系统实验箱系统简介:

TRY-CMX16+现代计算机组成原理与系统结构是以广受赞誉的经典产品 TRY-CPT16十六位机(FPGA)扩展实验板为基础研制的第三代面向教学实践领域的计算机应用类实验系统。该计算机实验系统字长16位,以系统结构与原理组成为基础,综合接口应用,涉及CPLD/FPGA器件设计,知识面宽、适用范围广泛。

二、现代计算机原理与系统实验箱体系结构

系统可按通用计算机的标准设计原理计算机,把模型机的构造特性与8086/8051相兼容。系统对于“定长指令”仅从指令格式分类的角度举例验正,动态的体系结构彻底摆脱了非标准实验环境下特定和虚构的不规范语言给原理计算机语言教学实践活动所带来的困扰。

三、现代计算机原理与系统实验箱指令构造

TRY-CMX16+的指令格式采用“变长指令字”结构,不同指令操作码不完全相同,操作码的位数不固定,结构灵活,减少指令码冗余,提高执行效率,能充分利用指令码所有位,最多可以设计256条指令。在达爱思通用汇编器的支撑下,既可设计属于您自己的个性化指令系统,亦可设计成与16/8位微处理器兼容的标准指令系统,为模型计算机的通用化设计构建了一个可操作平台。

微控制器

TRY-CMX16+运用“PLA”理念,用存储器逻辑与组合逻辑相结合的方法构造微控制器,根据程序需要自动变更当前控制逻辑,对于使用频率高的简单指令以及很有用又不复杂的指令选择组合逻辑,遇复杂的、不规整需扩充的指令选择存储器逻辑,从而实现动态计算机体系结构。

后续微址

微程序控制器中隐含后续微地址(BAF),采用断定法,由转移控制段BCF(2位)规定后续微地址形成方式,支持顺序执行(uPC+1),进位位转移,零标志转移,无条件转移,在取指周期以操作码形成后续微地址。

四、现代计算机原理与系统实验箱时序层次

TRY-CMX16+拥有一个周期、节拍、脉冲组成的三级时序系统。以取指周期为始设了四个状态触发器,在组合逻辑控制中,该触发器为1,控制器进入那个机器周期的微操作。系统按序定拍,随机器周期动态变更节拍发生器,在非取指周期产生T1→T3→T4三拍制节拍发生器,在取指周期产生T1→T2→T3→T4四拍制发生器。

卓越的软硬件环境

实时部件显示:各部件单元都以计算机结构模型布局,清晰明了,各部件均有七段数码管显示其十六进制内容。两个数据流方向指示灯以直观反映当前数据的来源与目标去向。即使不借助PC机也可实时观察数据流状态,判断其正确性,提供一目了然的实验环境。

开放式设计:系统支持三种实验电路构造方式,即实验单元电路的硬布线连接方式、单元电路的控位连接方式和实验电路“软连线”方式。对于实验单元电路的硬布线连接方式,可采用双头实验导线从零开始在扩展区域逐一搭起一个实验电路;对于各单元电路的控位连接,只需使用双头实验导线在单元电路控位与控制信号之间对应连接,就可构造出实验所需的部件控制电路;亦可使用可编程逻辑器件在线设计下载实验电路,实现实验电路的“软接线”。

逻辑分析:对于教师而言,不难体会要讲清时序关系是不容易的,而学生理解并利用时序关系则难上加难。而由于现代集成技术的迅猛发展,在实际工作中需要更多的利用逻辑分析工具进行时序分析。达爱思计算机组成原理教学实验系统具备逻辑分析功能,老师可通过电化教学设备向学生现场展示指令与时序的关系,让学生在实验时直观地观测到指令与时序的关系,有效的提高教学效果。

灵活的多操作方式

TRY-CMX16+以高性能MCU为核心组成系统的操作与控制平台,自带键盘、LCD显示,配备强大的集成开发环境,拥有前后台双环境支持,跟踪运行轨迹、受理中断请求、变更控制模式、捕捉现场信息。

主流处理器的多总线结构

系统采用多总线结构,分别是数据总线、指令总线、微总线。这种三者分离并行的总线结构,遇取指周期可以并行完成操作数的存取,在当前指令结束后的首个微周期可直接进入下一条指令的取指操作,通过微总线形成电路解释与执行的后续微址,因此指令总线与微总线的主要仼务是预取指与后续微址的预处理。

FPGA开发支持,提供所有VHDL例程

系统可选配Xilinx的XCV200扩展板,具有20万门大规模FPGA用于CPU模型的设计,16位64K的RAM用于存放用户程序及数据。学生将设计好的CPU模型下载到FPGA,并将需要运行的程序下载到RAM,根据先易后难的实践思路逐步完成16位机、32位机的设计。

五、现代计算机组成原理与系统实验箱实验项目

|

运算器实验 |

通用寄存器实验 |

|

准双向I/O口实验 |

地址总线组成实验 |

|

十六位数据总线实验 |

存储器读写实验 |

|

指令总线运用实验 |

中断控制实验 |

|

微控制器实验 |

时序部件实验 |

|

FPGA设计实验(需选配XCV200扩展板)采用Xilinx公司的20万门FPGA器件XCV200与16位64K的RAM,构成模型计算机CPU+程序数据存储器。 |

16位ALU实验 |

|

16位寄存器实验 |

16位指令计数器PC实验 |

|

中断控制实验 |

手动综合示教实验 |

|

8086微控制器示教实验 |

典型模型机实验 |

|

基本模型机的设计与实现 |

分段模型机的设计与实现 |

|

带移位运算的模型机的设计与实现 |

复杂模型机的设计与实现 |

|

流水模型机的设计与实现 |

基于RISC处理器构成模型机实验 |

|

基于重叠技术构成的模型机实验 |

中断模型机的设计与实现 |

|

PLA综合模型机的设计与实现 |

通用计算机实验 |

|

MCS-51单片机的设计与实现 |

8086微处理器的设计与实现 |

|

微机接口实验(需选配CMIO扩展板) |

61C256存储器扩展 |

|

8253定时/计数器扩展 |

8251串行通信扩展 |

|

8259中断控制器扩展 |

8237可编程DMA控制器扩展 |